# **Technical Report**

### Timing Analysis of an Embedded Architecture for a Real-Time Power Line Communications Network

António Barros

HURRAY-TR-090301 Version: 1 Date: 23-03-2009

#### Timing Analysis of an Embedded Architecture for a Real-Time Power Line Communications Network

António Barros

IPP-HURRAY! Polytechnic Institute of Porto (ISEP-IPP) Rua Dr. António Bernardino de Almeida, 431 4200-072 Porto Portugal Tel.: +351.22.8340509, Fax: +351.22.8340509 E-mail: http://www.hurray.isep.ipp.pt

#### Abstract

Although voice and data transmission over power-lines is not a recent technology, the use of this medium to support time-constrained communications is still a subject of research. In the scope of an European R&D project (REMPLI - Real-time Energy Management via Powerlines and Internet) a new communication architecture was proposed, based on a two-level hierarchic system (medium-voltage and low-voltage). In order to support the required network previsibility and efficiency requirements, one of the project partners developed a new embedded architecture based on the Hyperstone's processor HyNet32XS interfacing with a power-line chipset (DLC-2C). The uClinux operating system was ported for this architecture to support the development of the new software architecture. Due to the architecture characteristics and the (multi)master/slave behaviour of the medium access layer, new packet routing and scheduling protocols – fundamental for the correct functioning of the network – were specified. In this context, the main objective of this dissertation is to study the timing behaviour of the timing behaviour of these new protocols.

Keywords: Real-time networks, embedded systems, embedded Linux, power-line communications.

#### Timing Analysis of an Embedded Architecture for a Real-Time Power Line Communications Network

António Manuel de Sousa Barros

Dissertação submetida para satisfação parcial dos requisitos do grau de mestre em Eng. Electrotécnica e de Computadores (Área de especialização de Telecomunicações)

Dissertação realizada sob a supervisão de Professor Doutor António Miguel Pimenta Monteiro do Departamento de Engenharia Informática da Faculdade de Engenharia da Universidade do Porto e Doutor Luís Miguel Rosário Pinho

do Centro de I&D CISTER do Instituto Superior de Engenharia do Porto

Porto, Setembro de 2008

## Abstract

Although voice and data transmission over power-lines is not a recent technology, the use of this medium to support time-constrained communications is still a subject of research. In the scope of an European R&D project (REMPLI - Real-time Energy Management via Powerlines and Internet) a new communication architecture was proposed, based on a two-level hierarchic system (medium-voltage and low-voltage). In order to support the required network previsibility and efficiency requirements, one of the project partners developed a new embedded architecture based on the Hyperstone's processor HyNet32XS interfacing with a power-line chipset (DLC-2C). The uClinux operating system was ported for this architecture to support the development of the new software architecture.

Due to the architecture characteristics and the (multi)master/slave behaviour of the medium access layer, new packet routing and scheduling protocols – fundamental for the correct functioning of the network – were specified. In this context, the main objective of this dissertation is to study the timing behaviour of this architecture, focusing in the behaviour of the routing and scheduling protocols. Particularly important is the validation of the timing behaviour of these new protocols.

Keywords: Real-time networks, embedded systems, embedded Linux, power-line communications.

## Sumário

Embora a transmissão de voz e dados em redes eléctricas (Power-line Communication) não seja uma tecnologia recente, a sua utilização para suportar comunicação com requisitos temporais é ainda foco de investigação. Para esse efeito, no âmbito de um projecto europeu (REMPLI - Real-time Energy Management via Powerlines and Internet) foi proposta uma nova arquitectura de comunicação num sistema hierárquico de dois níveis (média tensão e baixa tensão). Devido às características da arquitectura e ao comportamento (multi)mestre-escravo da camada de acesso ao meio, foram especificados novos protocolos de encaminhamento e escalonamento de pacotes, fundamentais para o correcto funcionamento da rede.

De forma a suportar os requisitos de previsibilidade e eficiência da rede, foi desenvolvida por um dos parceiros do Projecto uma nova arquitectura de processamento embebida baseada no processador HyNet32XS da Hyperstone e no módulo de comunicações sobre linhas de transmissão eléctrica DLC-2C. Para suporte, o sistema operativo uClinux foi portado para esta arquitectura.

A validação das características temporais desta arquitectura é um factor de relevância na validação dos resultados do projecto. Mais ainda, a validação do comportamento temporal dos novos protocolos de encaminhamento e escalonamento de pacotes é um factor imprescindível para o sucesso do projecto. Neste âmbito, o objectivo desta dissertação é o de estudar o comportamento temporal desta arquitectura, especificamente para suportar os protocolos de encaminhamento e escalonamento desenvolvidos no projecto.

**Palavras-chave:** Redes de comunicações de tempo-real, sistemas embebidos, comunicações via linha de transmissão eléctrica, *embedded linux*.

## Acknowledgements

It is impossible to refer every person and institution worthy of my acknowledgement for helping me carry this dissertation through, but for the exceptional value of their support, some persons are impossible not to mention.

First of all I would like to express my gratitude to my supervisors: Miguel Pinho for giving me the opportunity to participate in this challenging project, his outstanding supervision, the invaluable advice, the permanent pressure to never miss deadlines, and Professor Miguel Monteiro for his interest in my work, his extraordinary generosity and helpfulness in the guidance of this dissertation and for all the support given during the period this work lasted.

I want to thank all the people in IPP-HURRAY! Research Group, at the School of Engineering of the Polytechnic Institute of Porto, for creating such a challenging and motivating environment for technology innovation. A special word for my team colleagues Filipe Pacheco and Luís Marques for making team work so easy, pleasant and stimulating!

I would like to thank Maksim Lobashov from Institute of Computer Technology at the Vienna University of Technology, for his collaboration during integration.

I would also like to thank my parents for the constant love and support during all my life, and encouragement to never stop improving myself.

And, finally, a very special thanks to Dulce, for all the love and encouragement, and clearing my skies whenever they are dark and clouded!

## Contents

| 1 | Intro                | oduction                               | 1        |  |  |  |  |

|---|----------------------|----------------------------------------|----------|--|--|--|--|

|   | 1.1                  | Research objectives                    | 3        |  |  |  |  |

|   | 1.2                  | Contributions                          | 3        |  |  |  |  |

|   | 1.3                  | Structure of this dissertation         | 3        |  |  |  |  |

| 2 | Con                  | itext                                  | 5        |  |  |  |  |

|   | 2.1                  | Embedded systems                       | 5        |  |  |  |  |

|   |                      | 2.1.1 Embedded software development    | 7        |  |  |  |  |

|   | 2.2                  | Embedded system architectures          | 9        |  |  |  |  |

|   |                      | 2.2.1 Cell phone                       | 9        |  |  |  |  |

|   |                      | *                                      | 0        |  |  |  |  |

|   |                      |                                        | 1        |  |  |  |  |

|   |                      |                                        | 3        |  |  |  |  |

|   | 2.3                  | ······································ | 4        |  |  |  |  |

|   | 2.4                  |                                        | 6        |  |  |  |  |

|   | 2.5                  |                                        | 8        |  |  |  |  |

|   | 2.0                  |                                        | 8        |  |  |  |  |

|   |                      | C                                      | 9        |  |  |  |  |

|   |                      | -                                      |          |  |  |  |  |

| 3 | Embedded platform 21 |                                        |          |  |  |  |  |

|   | 3.1                  |                                        | 21       |  |  |  |  |

|   | 3.2                  | I I I I I I I I I I I I I I I I I I I  | 22       |  |  |  |  |

|   |                      | 3.2.1 Operating system                 | 22       |  |  |  |  |

|   |                      | 3.2.2 Programming tools                | 23       |  |  |  |  |

|   |                      | 3.2.3 Kernel space / User Space        | 23       |  |  |  |  |

| 4 | REN                  | MPLI Transport Layer 2                 | 25       |  |  |  |  |

|   | 4.1                  |                                        | 25       |  |  |  |  |

|   |                      | -                                      | 27       |  |  |  |  |

|   |                      | 1                                      | 27       |  |  |  |  |

|   | 4.2                  |                                        | 28       |  |  |  |  |

|   | 4.3                  | · · · · · · · · · · · · · · · · · · ·  | 29       |  |  |  |  |

|   |                      |                                        | -        |  |  |  |  |

|   | 4.4                  | The Transport Route Manager            | 50       |  |  |  |  |

|   | 4.4                  | I S S                                  | 30<br>30 |  |  |  |  |

| 5  | Transport Layer implementation |                                                                   |    |

|----|--------------------------------|-------------------------------------------------------------------|----|

|    | 5.1                            | Mapping the Simulation module                                     | 33 |

|    |                                | 5.1.1 Simulating the REMPLI system: a brief introduction          | 33 |

|    |                                | 5.1.2 Parallel development of Simulation and Implementation       | 35 |

|    |                                | 5.1.3 Keeping source code simultaneously C and C++ compatible     | 37 |

|    | 5.2                            | Architecture of the implemented TL                                | 41 |

|    | 5.3                            | Concurrent processing                                             | 43 |

|    |                                | 5.3.1 Polling the message queues                                  | 44 |

|    |                                | 5.3.2 Multithreading the modules                                  | 45 |

|    | 5.4                            | Intermodule communications                                        | 46 |

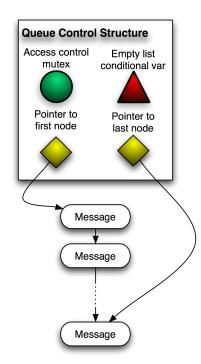

|    |                                | 5.4.1 Queue Control Structure                                     | 46 |

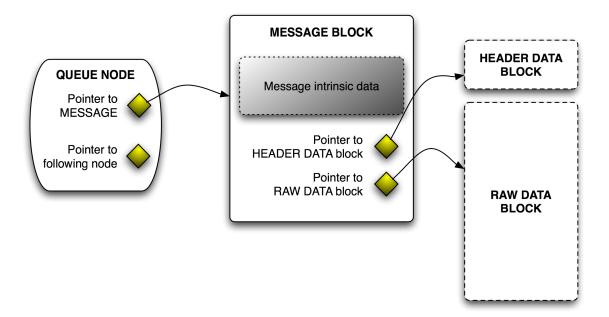

|    |                                | 5.4.2 Message queue nodes                                         | 48 |

|    |                                | 5.4.3 Scheduled Messages Service                                  | 50 |

|    |                                | 5.4.4 Timer Service messages                                      | 51 |

|    | 5.5                            | Processing communications with the Driver DeMux                   | 51 |

|    |                                | 5.5.1 Handling the Command channels                               | 53 |

|    |                                | 5.5.2 Serving the Notification channel                            | 54 |

|    |                                | 5.5.3 Distributing TL messages to channel handlers                | 55 |

|    | 5.6                            | Processing communications with the NL                             | 55 |

|    | 5.7                            | Heartbeat                                                         | 57 |

| 6  | Ana                            | lysis and evaluation                                              | 59 |

|    | 6.1                            | Message queue operations                                          | 61 |

|    | 6.2                            | Message processing                                                | 65 |

|    | 6.3                            | TL performance                                                    | 68 |

| 7  | Con                            | clusions and future work                                          | 73 |

|    | 7.1                            | Summary of this dissertation                                      | 73 |

|    | 7.2                            | Main contributions                                                | 75 |

|    |                                | 7.2.1 Characterisation of the REMPLI Transport Layer architecture | 75 |

|    |                                | 7.2.2 Implementation of a prototype of the REMPLI Transport Layer | 75 |

|    |                                | 7.2.3 Efficiency and predictability analysis of the REMPLI TL     | 75 |

|    | 7.3                            | Future work                                                       | 76 |

| Bi | bliogi                         | raphy                                                             | 77 |

## **List of Figures**

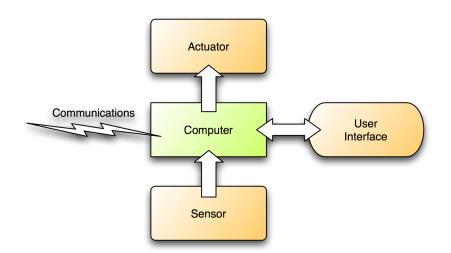

| 2.1  | Typical interfaces on an embedded system.                             | 6  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Nokia N82. Photo credit: Nokia.                                       | 10 |

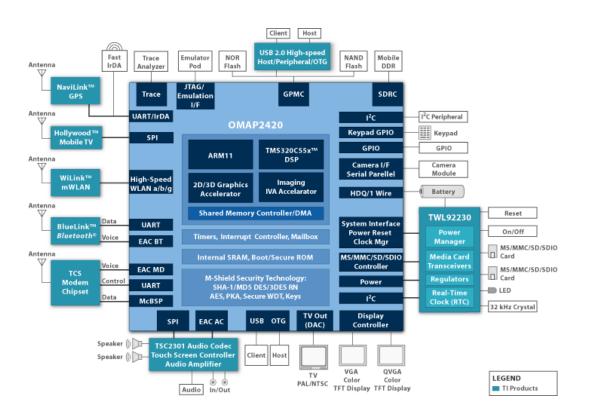

| 2.3  | OMAP 2420 block diagram. Graphic credit: Texas Instruments.           | 11 |

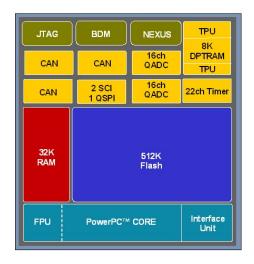

| 2.4  | MPC563 block diagram. Graphic credit: Freescale Semiconductor.        | 12 |

| 2.5  | Boeing 777. Photo credit: Boeing.                                     | 12 |

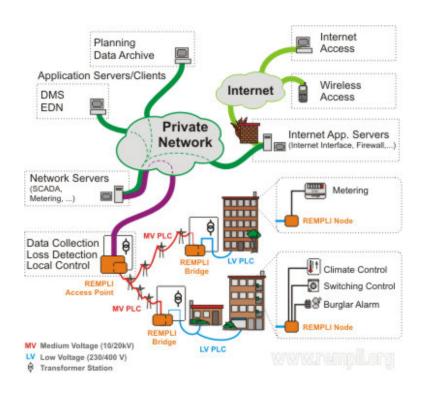

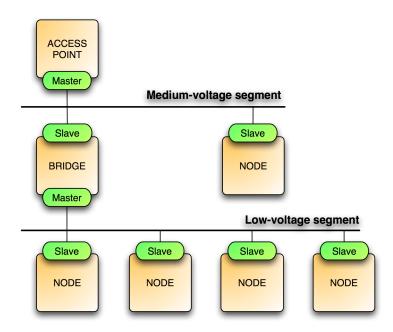

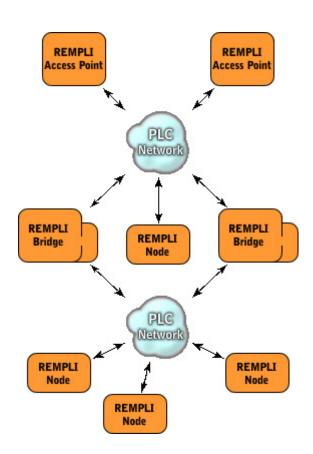

| 2.6  | REMPLI system architecture.                                           | 15 |

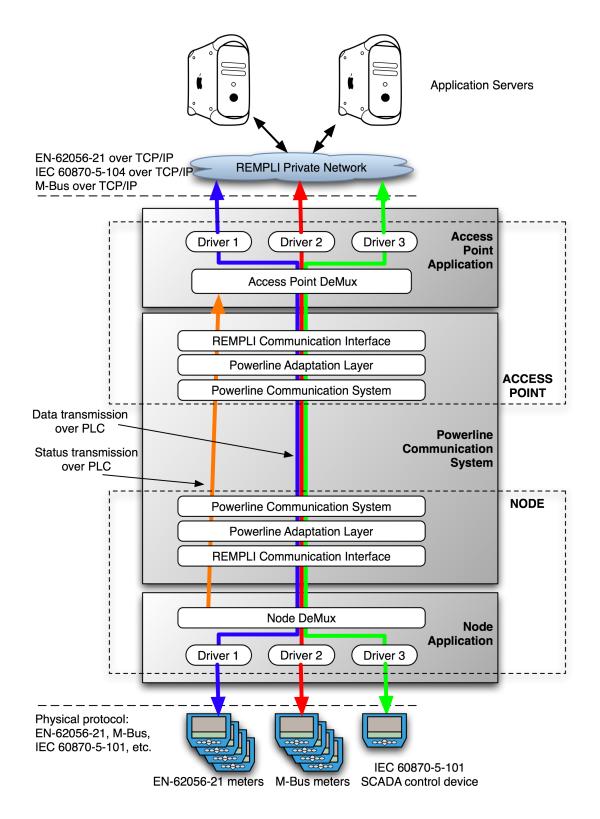

| 2.7  | REMPLI communications architecture over PLC.                          | 17 |

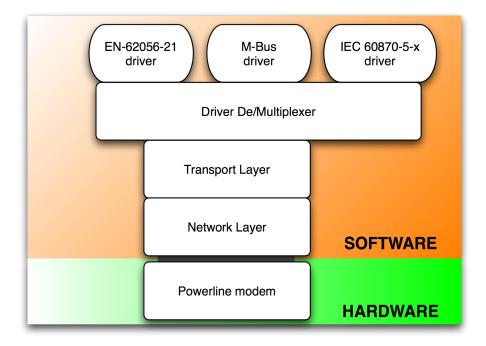

| 2.8  | Communication software building blocks.                               | 20 |

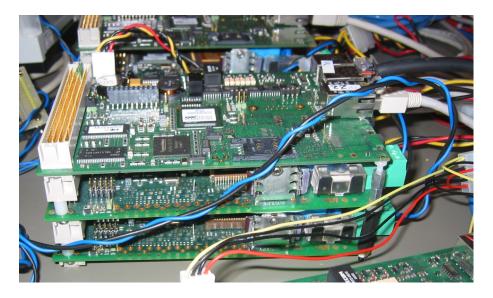

| 3.1  | REMPLI Bridge prototype                                               | 22 |

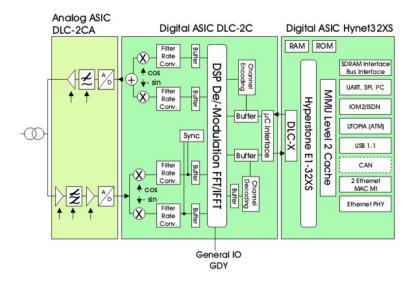

| 3.2  | DLC-2C/CA and hyNet 32XS integration (courtesy iAd GmbH)              | 23 |

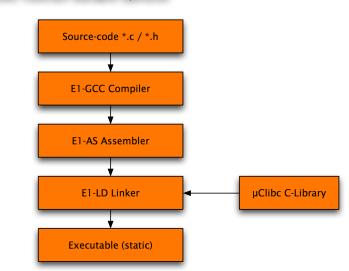

| 3.3  | Application build sequence of operations (courtesy iAd GmbH)          | 24 |

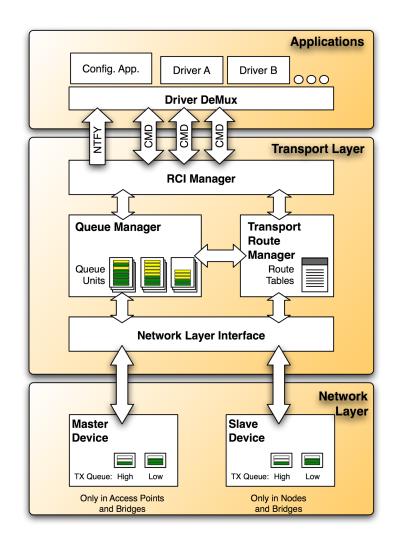

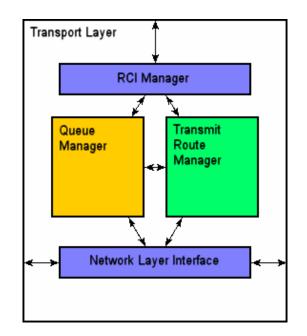

| 4.1  | Transport Layer integration with other communications software        | 26 |

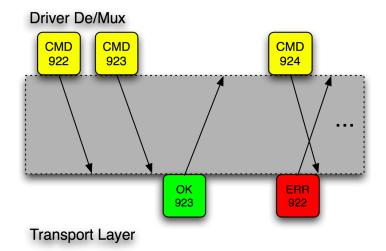

| 4.2  | Timing perspective of Commands and Responses over one Command channel | 28 |

| 4.3  | Master and Slave devices in REMPLI devices on the network.            | 29 |

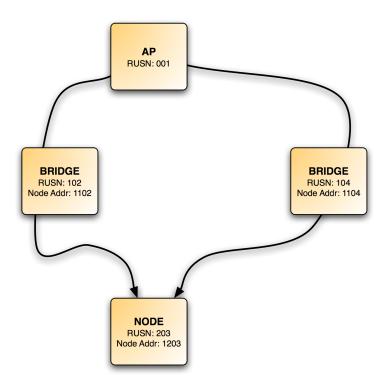

| 4.4  | Two possible routes to reach Node 203                                 | 31 |

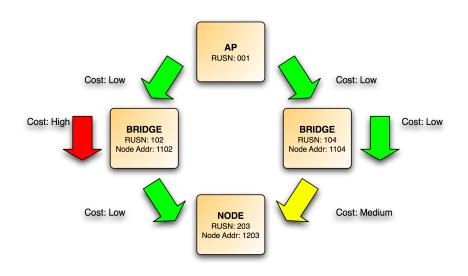

| 4.5  | Route cost estimation                                                 | 32 |

| 5.1  | A REMPLI Bridge TL model (graphic captured from OMNeT++)              | 34 |

| 5.2  | A sample simulation REMPLI network (graphic captured from OMNeT++)    | 35 |

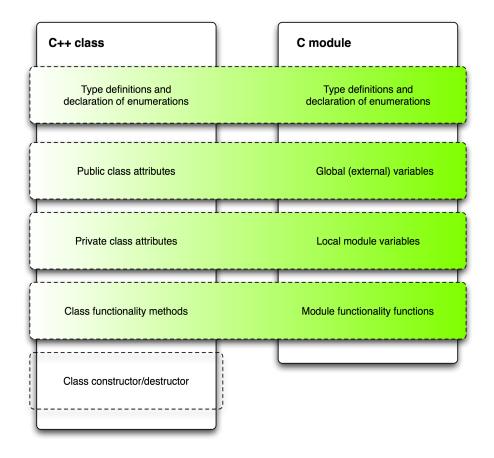

| 5.3  | Mapping a TL component C++ class into a C module                      | 36 |

| 5.4  | TL components and internal services.                                  | 42 |

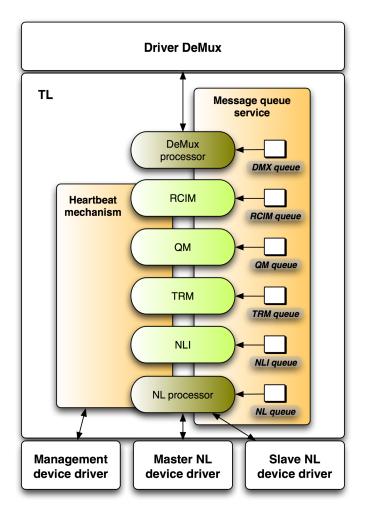

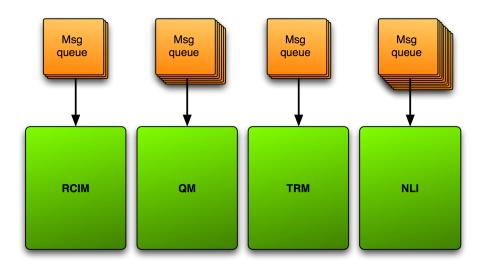

| 5.5  | Each TL module receives tasks from its corresponding message queue    | 44 |

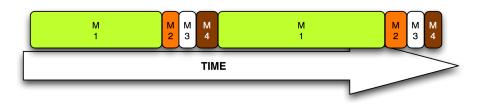

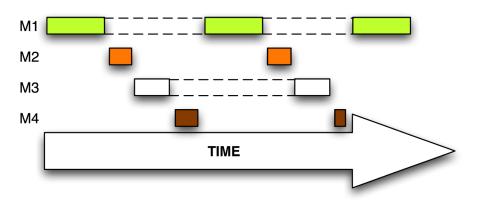

| 5.6  | Module M1 uses more time than the remaining modules                   | 45 |

| 5.7  | Multithread perspective of modules' executions                        | 46 |

| 5.8  | Message queue and respective Queue Control Structure                  | 47 |

| 5.9  | Message component building blocks                                     | 48 |

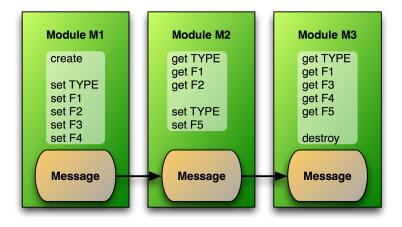

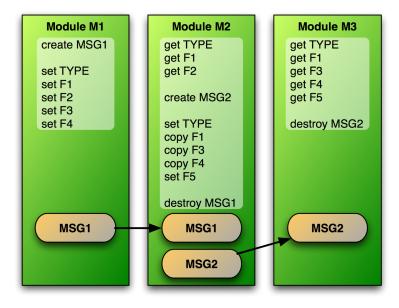

| 5.10 | Sequence of operations with persistent "fits-all" message             | 49 |

| 5.11 | Same sequence as Figure 5.10 with optimized-structure messages        | 50 |

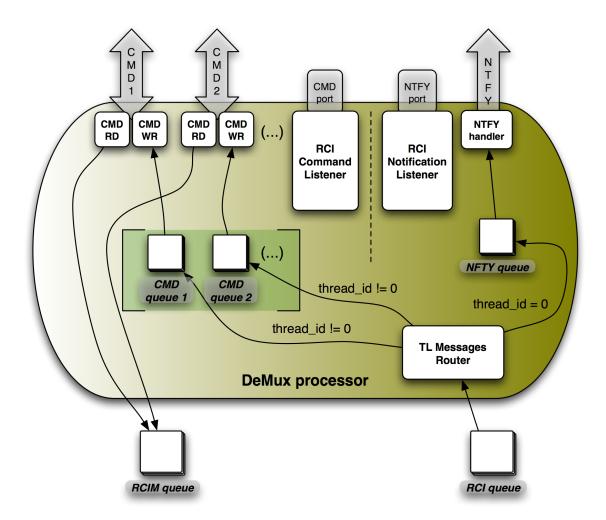

| 5.12 | DeMux processor general view                                          | 52 |

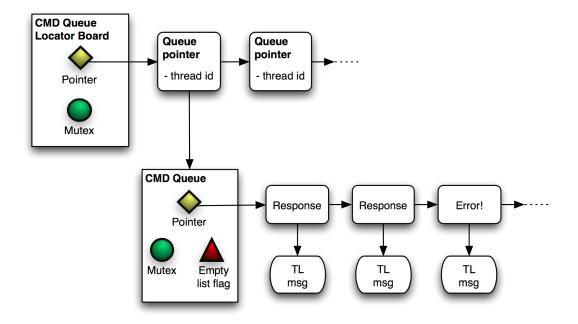

|      | Mechanism to locate Command Queues                                    | 54 |

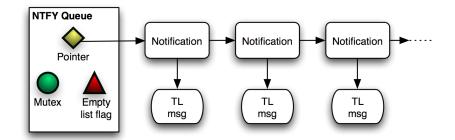

| 5.14 | Perspective of the NTFY Queue.                                        | 55 |

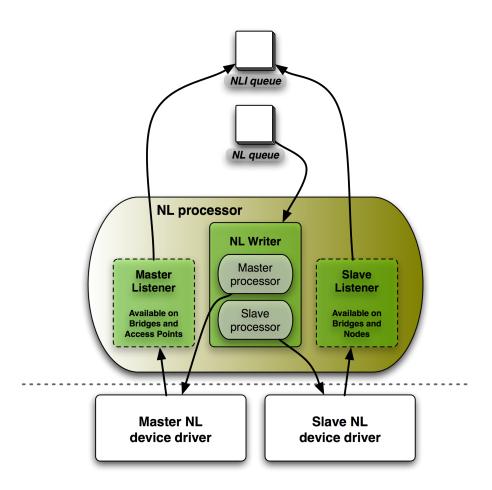

|      | NL processor details.                                                 | 56 |

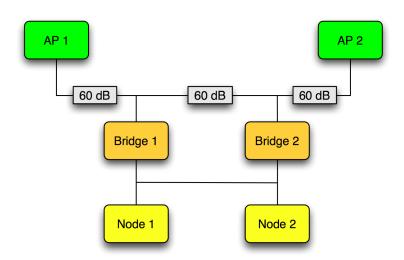

| 6.1  | Diagram of the REMPLI testbed                                         | 60 |

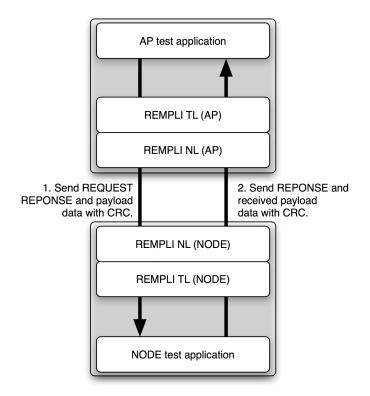

| 6.2  | TL performance test scheme.                                           | 61 |

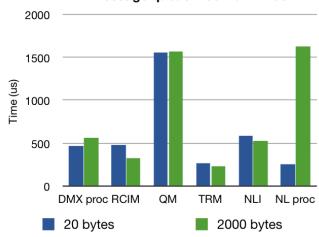

| 6.3  | AP average message queue insertion times.                             | 63 |

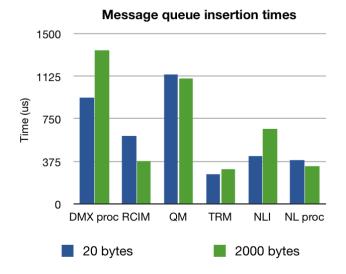

| 6.4 | Node average message queue insertion times.         | 64 |

|-----|-----------------------------------------------------|----|

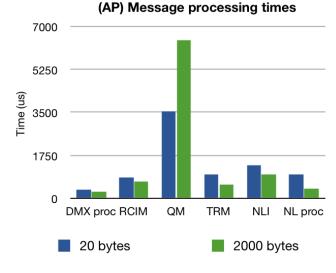

| 6.5 | AP average message processing times.                | 66 |

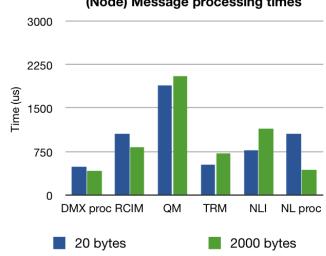

| 6.6 | Node average message processing times               | 68 |

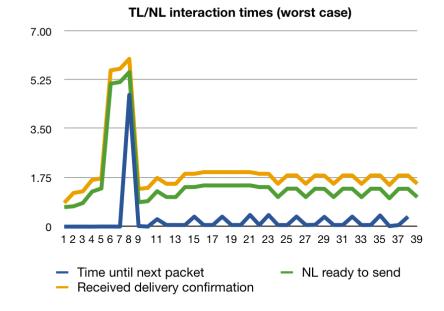

| 6.7 | NL packet time responsiveness (worst case recorded) | 69 |

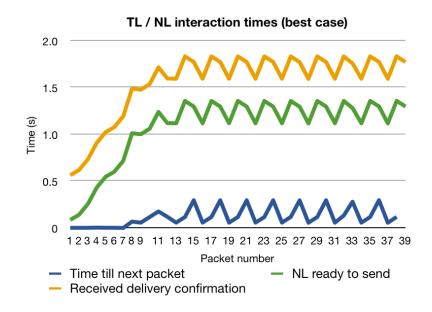

| 6.8 | NL packet time responsiveness (best case recorded)  | 71 |

## **List of Tables**

| 6.1  | Insertion times for AP, 20 bytes SENDREQRESP        | 62 |

|------|-----------------------------------------------------|----|

| 6.2  | Insertion times for AP, 2000 bytes SENDREQRESP.     | 62 |

| 6.3  | Insertion times for Node, 20 bytes SENDRESP         | 63 |

| 6.4  | Insertion times for Node, 2000 bytes SENDRESP       | 64 |

| 6.5  | Processing times for AP, 20 bytes SENDREQRESP       | 65 |

| 6.6  | Processing times for AP, 2000 bytes SENDREQRESP.    | 66 |

| 6.7  | Access Point QM times to fragment SENDREQRESP data. | 67 |

| 6.8  | Processing times for Node, 20 bytes SENDRESP.       | 67 |

| 6.9  | Processing times for Node, 2000 bytes SENDRESP      | 67 |

| 6.10 | Node QM times to fragment SENDRESP data.            | 68 |

| 6.11 | TL response times on a REMPLI AP                    | 69 |

# List of acronyms

| ABI     | Application Binary Interface                            |

|---------|---------------------------------------------------------|

| ACE     | Actuator Control Electronics                            |

| ΑΡΙ     | Application Programming Interface                       |

| ASIC    | Application-Specific Integrated Circuit                 |

| АТМ     | Asynchronous Transfer Mode                              |

| CAN     | Controller Area Network                                 |

| CENELEC | European Committee for Electrotechnical Standardization |

| COTS    | Commercial-Of-The-Shelf                                 |

| CPU     | Central Processing Unit                                 |

| CRC     | Cyclic Redundancy Check                                 |

| DeMux   | Demultiplexer/Multiplexer                               |

| DSP     | Digital Signal Processor                                |

| ECU     | Electronic Control Unit                                 |

| EN      | European Standard                                       |

| FBW     | Fly By Wire                                             |

| FEC     | Forward Error Correction                                |

| FIFO    | First In, First Out                                     |

| FPGA    | Field-Programmable Gate Array                           |

| GPRS    | General Packet Radio Service                            |

| GSM     | Global System for Mobile communications                 |

| IC      | Integrated Circuit                                      |

| IEC     | International Electrotechnical Commission               |

| Ю       | Input/Output                                            |

|         |                                                         |

| IP         | Internet Protocol                                        |

|------------|----------------------------------------------------------|

| IPCTransID | Inter Process Communication Transaction Identifier       |

| ISA        | Instruction Set Architecture                             |

| ISDN       | Integrated Services Digital Network                      |

| ISO        | International Organization for Standardization           |

| ITU        | International Telecommunication Union                    |

| IVA        | Imaging and Video Accelerator                            |

| LLC        | Logical Link Control                                     |

| MAC        | Media Access Control                                     |

| NFS        | Network File System                                      |

| NL         | Network Layer                                            |

| NLI        | Network Layer Interface                                  |

| OFDM       | Orthogonal Frequency Division Multiplexing               |

| 00         | Object Oriented                                          |

| OS         | Operating System                                         |

| OSI        | Open Systems Interconnection                             |

| PFC        | Primary Flight Computer                                  |

| PDU        | Protocol Data Unit                                       |

| PLC        | Power-Line Communication                                 |

| POSIX      | Portable Operating System Interface                      |

| POTS       | Plain Old Telephone Service                              |

| QM         | Queue Manager                                            |

| RCI        | REMPLI Communication Interface                           |

| RCIM       | RCI Manager                                              |

| REMPLI     | Real-time Energy Management via Power-Lines and Internet |

| RISC       | Reduced Instruction Set Computer                         |

| RS         | Recommended Standard                                     |

| RTOS       | Real-Time Operating System                               |

| RUSN       | REMPLI Unique Serial Number                              |

#### xiii

| SCADA | Supervisory Control And Data Acquisition    |

|-------|---------------------------------------------|

| SoC   | System-on-a-Chip                            |

| ТСР   | Transmission Control Protocol               |

| TDMA  | Time Division Multiple Access               |

| TFTP  | Trivial File Transfer Protocol              |

| TL    | Transport Layer                             |

| TRM   | Transport Route Manager                     |

| UART  | Universal Asynchronous Receiver/Transmitter |

| USB   | Universal Serial Bus                        |

### Chapter 1

## Introduction

The use of the electrical power distribution grid as a communications medium for grid operation tasks – such as ripple control – started several decades ago, although classical applications were not too much demanding [1]. The higher dissemination of the electrical grid access, as compared to other native communication utilities, led to a recent trend of using it as transport medium of digital communications. However, the hostile physical characteristics of this medium for high data rates and frequency bands, verified on field tests, has reduced the will to use the electrical distribution grid for broadband applications.

Current energy distribution and management involves many tasks – such as load balancing, grid monitoring and reconfiguration – that require data acquisition, along with a supporting communication infrastructure. These tasks can be more effective if consumption measurement resolution can be spatially and temporally increased [1]. Native communication networks, such as Plain Old Telephone Service (POTS) and General Packet Radio Service (GPRS) are already used for Supervisory Control And Data Acquisition (SCADA) but the cost of these solutions often impair the dissemination of remote monitor and actuator equipment, which is only installed in central points, like transformer and supply stations [2]. Increasing the spatial resolution of the energy measurements would imply increased recurring costs if the same native communication media continue to be used. The omnipresent feature of power-line and the savings provided by an already deployed network are appealing enough for electricity distribution companies to push applications supported by the electrical power grid. Nevertheless, this medium is only effective if it guarantees the necessary data rates to provide the required timing resolution of remote measurements.

The Real-time Energy Management via Power-Lines and Internet (REMPLI) project (European program NNE5-2001-00825) [3] objective was to develop a distributed infrastructure suitable for real-time monitoring and control of energy consumption. In the short-term, this communication in-frastructure should support the operation of energy distribution networks and, in the medium-term it may be available to support additional services, even if some are yet not foreseen [4].

One of the primary goals of REMPLI is to provide the registration of energy consumption, not only from meters located at the costumer's premises but also from meters located at branching points of the distribution network, with higher timing resolution. Besides the cost saving advantages from automated remote meter reading and billing, the collected data can be statistically processed to identify fine-grained consumption patterns which are fundamental for effective planning of energy distribution networks. Real- or near real-time monitoring of the energy consumption can also permit the energy supplier to apply tariff schemes that condition the costumers to certain behaviours that may lead to a more rational use of the distribution network<sup>1</sup>. In a liberalised energy market, the REMPLI system can also be an useful tool for costumers and energy suppliers/distributors: as each meter can be remotely accessible to any energy company in the market, the costumer is no longer attached to a single company and can chose the contract that best suits the intended usage profile. Synchronous data collected from distributed meters can also be used in energy loss detection and faster detection of its source (leakage, short circuit or fraud).

Another primary goal of REMPLI is to provide a platform to support the management of distributed networks. The multiple types of data collected and transported by the REMPLI communication infrastructure permits the development of advanced energy management functions that can be employed by using remote/distributed control equipment.

Besides the immediate goals referred, the REMPLI system has an open-design that is scalable and allows the addition of new services that can be built on top of the system interface provided by REMPLI.

The underlying communication system is based on combined Power-Line Communication (PLC) and Internet network. The use of PLC technology is justified by the fact that, on one hand, most of the energy metering and control equipments are already wired to the low-voltage and/or mid-voltage electric networks, and, on the other hand, it is difficult to access certain equipments using wireless technology as they are often located in closed environments and/or with metallic obstacles (reinforced concrete walls and tubes).

In a wide-area PLC network, transmitting a packet from a source to a not immediately reachable destination requires the packet relay of intermediate nodes (repeaters). However, considering the dynamic topology change and impossible prediction of the power-line attenuation, repeaters cannot be statically configured [5]. How to design the efficient routing protocols for dynamically adapting the power-line circumstances and shortening the transmission time under stringent bandwidth limitation consists thus a challenging problem.

The REMPLI communication stack includes the *physical*, the *network*, the *transport* and the *application* layers [6]. The network layer implements a master/slave time division network, and short-distance routing mechanisms supported by node status tables. One network segment can hold multiple masters, operating in different time slots or different frequency bands, but a slave can be simultaneously connected to multiple masters if they operate in the same frequency band. The time division multiple access demands very strict timing requirements from the network layer.

The transport layer handles the end-to-end communication, providing inter-network routing, address translation, data fragmentation/assembling, request/response pairing and an alarm service. Masters know in real-time the status of associated slaves and calculate all possible paths for all active slaves. For each available path it is also calculated the link quality, taking in accounting the average delay and error rate. Besides the routing tasks, the transport layer is also responsible to adapt the variable-size application data to the network fixed-size packets, performing fragmentation at the source and assembling at the destination. Fragmentation can be a complex operation on bridges, when the two network segments the bridge connects have different packet sizes and the bridge cannot simply act as a repeater, but has to perform re-fragmentation instead.

When an application requests the transport layer to perform some task, the transport layer will later inform the application about the result of the request processing within a specific time limit. The timing requirements of the transport layer are not so strict as the timing requirements of the network layer but since the underlying communication network is narrowband and the available data rate is a valuable resource, the performance of the transport layer must be higher than the slowest component

<sup>&</sup>lt;sup>1</sup>Smoothing the production and network load profiles.

(the network), in order to not impair the whole system performance. In this way, the analysis of the timing requirements is absolutely necessary to verify the validity of this architecture.

#### **1.1 Research objectives**

The main objective of this dissertation is to analyse the timing behaviour of this set of complex protocols in the architecture's Transport Layer. Due to the complex functionality required from the REMPLI Transport Layer (TL) and its less restrictive time constrains<sup>2</sup>, this protocol layer was unusually developed as a user-space application. Nevertheless, and considering the narrow bandwidth the communications medium has, it is not admissible that the software components introduce additional delays, therefore it is necessary to verify if the complexity of the REMPLI TL implementation does not transform the implementation of this layer in the bottleneck of the complete system.

#### **1.2** Contributions

The specification of the REMPLI system introduces an increased complexity to what is common in the transport layer of generic communication protocol stacks. The routing and scheduling algorithms developed within the project were proven functional in a simulation environment, but a physical prototype must be implemented and validated in the field before a product being deployed.

This dissertation contributes to this overall goal providing:

- 1. an analysis of the REMPLI Transport Layer architecture;

- a fully functional prototype of the REMPLI Transport Layer for the specific architecture developed within the project;

- efficiency and predictability analysis of the REMPLI Transport Layer, in the embedded architecture developed during the project.

This prototype is to be deployed in a field test to verify the validity of the routing and scheduling protocols in real-life conditions, and should serve as basis of the final commercial product.

#### **1.3** Structure of this dissertation

This dissertation is divided into 7 chapters, as follows.

Chapter 2 provides an overview of real-time embedded systems and development methodologies. In this context, the chapter also presents an overview of the REMPLI system and a description of communication and software architectures.

Chapter 3 gives an insight of the hardware and software environments in which the REMPLI system executes. The hardware was developed specifically for this system, and a Linux kernel version for microcontrollers without a memory management unit was ported for this architecture. Along with the kernel port, a toolchain was also ported in order to allow the development of kernel extensions, device drivers and applications.

<sup>&</sup>lt;sup>2</sup>Compared with the time constrains associated with the Network Layer operation.

Chapter 4 then presents the details of the REMPLI Transport Layer, the main focus of this dissertation. The four main modules of this communication layer are introduced together with a detailed description of their functionality and of the services they provide.

Chapter 5 describes how the REMPLI TL was developed within the REMPLI architecture. This development started with simulation code which included the functionality of the four modules, and then was necessary to implement the mechanisms that allowed modules to execute concurrently and communicate both inside the layer and with the adjacent layers.

In real-time systems the timing behaviour is the top concern since the value of the computed result of the correct solution also depends on the time it is provided. Therefore, laboratory tests were conducted to assess the usefulness of the developed protocols. The results are presented and analysed in chapter 6.

Finally, this dissertation concludes with chapter 7, which summarizes the dissertation contributions and analyses its main conclusions. The chapter also identifies topics for future research that can be potentially explored.

### **Chapter 2**

## Context

#### 2.1 Embedded systems

An *embedded system* is a computer that is implemented for a specific purpose, frequently to control a larger system in which the computer is inserted [7]. Embedded systems have an innumerable range of applications, like pocket media players, vehicle electronic stability control, industrial process control or rocket guidance systems. Unlike a general purpose computer which may perform a wide range of tasks, the hardware design of an embedded system takes in consideration the limited set of tasks that will be performed, so the components are selected to fit the requirements. This hardware design allows to reduce the final unit cost, which is very important in large scale applications or in mass-production commercial products.

Embedded computers have to interact with the physical elements of the surrounding system by means of interface devices. Figure 2.1 represents the general type of interfaces that can be found on an embedded system. *Sensors* acquire data that allows the computer to estimate the status of the system like, for instance, a gyroscope in a rocket guidance controller. *Actuators* allow the computer to modify the system status, like attitude jets used to maintain a rocket in the trajectory. Embedded computers have reduced or none human interface because they are mostly used in applications that require small or none human intervention. Communications interfaces often are available as serial port and/or network adapter and are useful to control or monitor the embedded computer activity, to cooperatively exchange data with other embedded systems<sup>1</sup> or even use remote disk servers. It is also common that embedded systems without user interface have a console application that allows remote user interaction from another computer.

The main component in an embedded system is the *microcontroller*, which encapsulates in a chip the Central Processing Unit (CPU) with memory and other peripherals like I/O interfaces, timers and analog-to-digital converters. Depending on the application field of the embedded system, the CPU can be a processor from 4-bit up to 64-bit architecture. Memory in microcontrollers are of two types: volatile and non-volatile. The non-volatile is used to store the software that the embedded system will execute and the current trend is to be based on flash memory because it allows simple reprogramming of the embedded system. The volatile memory is used to store the application data and, in some cases, the on-chip memory is sufficient for the task (like in the anti-lock braking system of a car vehicle), but in more demanding cases, the computer must use external volatile memory.

Most embedded computers are intended to work under real-time constraints. In a real-time system,

<sup>&</sup>lt;sup>1</sup>Like the Electronic Stability Control system communicates with the Fuel Injection, Brake Control and Steering systems, whenever a vehicle is in risk of losing stability.

Figure 2.1: Typical interfaces on an embedded system.

an operation is considered valid only if it is supported by a correct calculation and is performed within a specific time period [8]. The strictness of the deadline of a real-time task can be divided in two categories [9]:

- A *hard real-time* task is a task that must be performed before the deadline, otherwise it will be valueless and will constitute a failure of the system like, for example, to activate the fire extinguishers in a transformer station when a fire is detected.

- A *soft real-time* task retains some value if performed after the deadline. For instance, when a remote household electricity meter reading takes longer than the specified timeout value, the request can be repeated without damage to the system, although the returned value is not as accurate as wanted.

Some real-time systems, like a nuclear power plant control system, have to cope with severe reliability requirements and any failure can be potentially catastrophic. A task that can lead to this situation if it misses the deadline is called *critical* and it must be assured that the task always makes its deadline, even under equipment failure or system workload. A combination of scheduling policies and equipment redundancy are employed to assure 100% that these critical tasks will never miss deadlines.

Depending on the size and complexity of the tasks, one of several embedded software architectures can be employed. For the least complex cases, a *control loop* calls routines that performs the required tasks. On a *interrupt controlled system*, each task routine is associated with a system interrupt and when the system receives one interrupt it triggers the execution of the respective interrupt handler. Under a *preemptive multitasking* architecture, tasks have access to the processor in controlled time slices. With more complex applications, an embedded system may use an operating system adapted for an embedded system, being controlled either by a microkernel or a monolithic kernel. The microkernel has reduced functionality which is complemented by processes executing in user-space. Oppositely, the monolithic kernel has a relatively large size but includes most of the facilities found in desktop systems which facilitates the development of software, at the expense of more computer resources and less predictability.

However, in more complex systems, such as REMPLI, the complexity and dimension of the system implies that the underlying embedded architecture is a full-fledged computer system. In this

case, embedded systems resort to more powerful hardware architectures and to adapted versions of general-purpose operating systems. There is, nevertheless, still the need to guarantee the hard real-time requirements of the control loops (and soft real-time requirements of the applications) and the interface to the surrounding system. This is one of the main challenges of the REMPLI architecture.

#### 2.1.1 Embedded software development

The advances in semiconductor technologies and associated decrease of processor cost and size has widened the application range of embedded systems. In the past, an embedded system would be small and simple, or probably a composition of few subsystems with barely none interaction. However, currently, the quantity and complexity of applications for embedded systems is growing rapidly, and the increasing computational power of processors is leading designers to allocate more functionality to software. All summed up, new challenges for embedded software development are being experienced in recent years. As an example, embedded electronics are believed to be responsible for 90% of innovation in the automotive products being 80% of that in the area of software [10]. The weight of embedded systems is also increasing: in aeronautics 50% of the cost of development of a new aeroplane stands for embedded hardware and software; in the automotive industry, embedded systems stand for 35% of a vehicle development costs (almost 40% of it standing for software), as opposed to the traditional 25% for power-train.

Real-time software development has to deal with constraints that are not considered on hosted systems, such as hard timing constrains, limited hardware resources, selected hardware platform, reliability and safety factors, cost factors and time-to-market, which require different development techniques [11]. Furthermore, in safety-critical systems, the timing behaviour of the implemented application is closely related to the hardware environment (*e. g.* processor, Operating System (OS) or communications network/bus). The increase in complexity required from real-time systems is challenging the traditional embedded software development techniques and productivity is decreasing, which is a serious problem when facing the tight time-to-market that are normal in some industrial fields.

In broad terms, a development process can be divided into 6 phases: Analysis, Specification, System Design, Implementation, Integration and Production [12]. Although currently these phases are not strictly sequential, their roles and tasks still hold.

The development of a new product starts with the description of the overall system behaviour, a high-level abstraction of system functionality completely independent from an implementation point of view [13]. Functional and non-functional requirements define how the system is expected to perform.

Based on the requirements, a functional specification is realised defining what has to be implemented. The specification is an objective description of the functionality of the system that does not imply an implementation. A specification usually contains a set of constraints that must be met and a set of design criteria that should be observed.

In large systems, the functionality of the system is modularly decomposed into subsystems. These subsystems may be developed in-house, or contracted to suppliers (which is frequent in automotive and aeronautic industries), so each subsystem will have its own functional specification that will be delivered to the respective developing team.

The specification of a product or subsystem is the starting point for the designer to select an hardware platform and devise algorithms that meet the functional requirements. In this way, the functional requirements and the experience of the designer are important factors when deciding the system architecture. The designer must also decide on which functions should be implemented on

hardware and which functions should be programmed as software.

The hardware platform selection is based in the intersection of specification constraints and semiconductor characteristics: the processor must meet a minimum speed and the memory must meet a minimum size. In recent years, there is a trend for Integrated Circuit (IC) manufacturers to prefer the production of chips that will serve for multiple designs, in order to balance development costs with the number of unit sales, reducing the range of options available. For some applications, the designers also have available Commercial-Of-The-Shelf (COTS) platforms. These factors may lead to an over-designed platform, but for a smaller cost. An over-designed platform also allows software updates and/or the addition of new functionalities that extend the application [13].

The implementation is the process in which the designed solution will become a practical product. During this phase, the programming team writes the software code for the target hardware. Right from the begining of the implementation, the programming team is limited by the characteristics of the platform architecture selected by the designer. Traditionally, in order to achieve the most efficient code, embedded source code was written using a low-level programming language, such as assembly or C, which would be assembled/compiled to generate the program that would run in the processor architecture. This method is very effective for simple applications, but writing code so dependent of a specific platform raises several problems in most of current applications.

- **Software complexity.** System designers are moving more and more functionality from hardware to software, claiming that software is more flexible to posterior corrections or extensions of functionality. This means that embedded software is being demanded to perform more functions of increasing complexity. Implementing extensive complex functionality in assembly on in "low-level" C is prone to increase the number of misconception errors.

- **Software reusability.** When the source code is too dependent of the specific platform architecture, it becomes very difficult to port it to a different platform architecture: this can happen even if the processor is replaced by another processor of the same family but with a modified Instruction Set Architecture (ISA). This issue is of particular importance when the life-cycle of the product is longer than the life-cycle of its components (hardware and software), and during production, warranty and after-sales assistance subsystems have to be replaced by newer technology [14]: *e. g.* during the life-cycle of an motorcar model, most electronic subsystems will be replaced by newer generation subsystems.

These issues have been addressed in recent years, in order to increase productivity of embedded software development and decrease the incidence of software errors. One of the most important steps is to create system standards that allow the independence of software from hardware components. A standardised Application Programming Interface (API) can hide diverse ISAs, providing a unified high-level interface to the hardware [14, 13]. This abstraction layer is supposed to include:

- a Real-Time Operating System (RTOS) that wraps the programmable cores and the memory subsystem, and provides a concurrency model;

- device drivers providing an interface to I/O subsystem services;

- a network communication service to provide applications access the network subsystem.

A practical example of this orientation is the Automotive Open systems Architecture (AUTOSAR) initiative [15]. Based on the Open Systems and the Corresponding Interfaces for Automotive Electronics (OSEK) specifications for an embedded operating system [16], the AUTOSAR defines a modular software architecture that supports hardware independence, so software can be reused in Electronic Control Unit (ECU) from different suppliers<sup>2</sup>, as long as adaptation middleware conforming to AU-TOSAR is provided. This means that software can be used in the same vehicle model, even the ECU supplier changes, and also that the same software module can be reused in other models (instead of being rewritten from scratch) [17], so new products may reach the market faster.

Integration refers to the phase in which all system components (hardware, software and communications network) are assembled and tested, and is probably phase that requires more time and effort [18]. During this phase the system should be exhaustively tested. Detected errors have then to be eliminated, and calibrations of subsystems may be necessary to correct deviations from the specified system behaviour.

Testing a distributed embedded system, in which several subsystems are connected by communication networks/buses can be a difficult task: unintentional feature interaction can occur, making the system respond in a unexpected manner under certain circumstances [17]. Another issue that requires deep analysis is the behaviour of the communications platform, specially if it can handle the amount of communications in a multiplexed medium accessed by multiple applications executing in parallel, each with specific time constraints, and every network node does not exhibit jitter.

Once the product prototype is considered ready for market, it starts the production. During the product life-cycle, some factors may require software updates: error patches, add or improve functionality, or maybe adapt the source code to a new generation of hardware platform.

#### **2.2 Embedded system architectures**

In order to exemplify the diversity of systems, this section presents four practical cases of real-time systems. The real-time systems presented range from a small-sized device with large-production and short lifecycle such as a smartphone, to a large production but safety-critical system such as automotive, a mission-critical and high-priced airliner and, finally, a industrial control system.

#### 2.2.1 Cell phone

Since the first GSM network was launched in 1991, that mobile phone devices have been disseminated to millions of costumers worldwide. Technological-push due to advances in more spectral-efficient modulations and semiconductors in combination to market-pull for new services are responsible for the incredible evolution of mobile phone devices: from the initial devices capable of voice-calls and text messaging (Short Message Service), to the current multimedia devices capable of playing music, carrying out video-calls, Internet access, digital TV reception and GPS navigation. In 2002 appeared the first GSM mobile phones with a imaging camera and other productivity applications such as an organizer, e-mail client and desktop computer synchronization, and since then two profiles of smartphones have emerged: business-oriented phones and multimedia phones. Both profiles present similar hardware characteristics, but part of the included applications differ in functionality.

The Nokia N82, depicted in Figure 2.2, is a smartphone announced as a "multimedia portable computer" [19] and released in late 2007. This cell phone is driven by the Texas Instruments OMAP 2420 processor, based on the 32-bit ARM11 architecture, running at the speed of 330 MHz [20]. This processor, represented in Figure 2.3 holds two cores:

the ARM1136 CPU running at 330 MHz, for general processing, and

<sup>&</sup>lt;sup>2</sup>Obviously as long as the application constraints are met.

Figure 2.2: Nokia N82. Photo credit: Nokia.

**the TI TMS320C55x**<sup>TM</sup>**Digital Signal Processor (DSP)** running at 220 MHz, for heavy signal processing tasks required by 3G applications like videocalls or Digital Video Broadcast - Handheld (DVB-H).

The OMAP 2420 processor also includes a 2D/3D graphics accelerator for image rendering and a Imaging and Video Accelerator (IVA) for video encoding and decoding at rates up to 30 frames per second.

The Nokia N82 has a 128 MB of SDRAM, which provides approximately 90 MB of free executable RAM, after boot up.

The operating system that manages the N82 resources is the Symbian OS v9.2, based on the S60 3rd Edition platform, Feature Pack 1. Symbian is an open operating system designed for mobile phones, and has a real-time microkernel architecture that executes exclusively in ARM processors. It contains features such as preemptive multitasking, memory protection, and perfectly copes with multicore processors.

#### 2.2.2 Automotive

Effective electronic systems started being introduced in automotive vehicles in the 1970's decade. The first system developed was the Electronic Fuel Injection, but various others – like the anti-lock braking system and the airbag system – soon began to be adopted by the automotive manufacturers. Recently, car vehicles have been evolving from an assemble of highly modularised embedded subsystems with small or none intercommunication between them, to a highly integrated system with large amounts of data being exchanged between the diverse ECUs, in order to provide new security and comfort features.

One practical example is the Mercedes-Benz S Klasse model released in late 1999 – the W220 – which contained more than 50 ECUs interconnected by 3 different bus systems, exchanging 150 types of messages and 600 signals [21]. One of the most important ECUs in a car is the Engine Control Unit, and on S Klasse vehicles motorised with the 3.2 liter V6 diesel engine (the S 320CDI V6), the Engine Control Unit is the Bosch EDC16CP31. This ECU is powered by the high-performance Freescale MPC563, a 32-bit PowerPC microcontroller that can operate at a clock speed range from 40 to 66 MHz, equipped with 64-bit floating-point unit [22] which is fundamental to cope with the complex computations performed on the multiple engine floating point parameter values. As represented in Figure 2.4, MPC563 holds 512KB of flash memory and 32KB of RAM; despite the in-chip flash memory, the ECD16CP31 ECU includes a M58BW016DB chip which provides 16 Mbit (512kbit x32) [23] of external flash, over a 32-bit data bus. The MPC563 also contains 3 CAN 2.0B bus modules

Figure 2.3: OMAP 2420 block diagram. Graphic credit: Texas Instruments.

for communication with other devices, and two queued 10-bit analog-to-digital converter modules (QADC64E\_A, QADC64\_B) providing a total of 32 analog channels.

#### 2.2.3 Airliner

Aircraft flight control systems include the flight control surfaces, the pilot controls at the cockpit and connecting linkages. Classical flight control systems can be mechanical in which the pilot controls are linked to the control surfaces by mechanical parts or hydromechanical in which hydraulic circuits transmit the pilot commands to the control surfaces. These classical systems pose several restrictions of design because require careful planning for parts placement and routing of links, and are heavy. The transmission of commands by electrical control circuits and computers, known as Fly By Wire (FBW), allows more versatility in design and saves weight. In 1987, the Airbus 320 was the first commercial airliner to fully employ this concept.

The Boeing 777, illustrated in Figure 2.5, entered into service in June 1995 and is currently the largest twinjet in service. The 777 is the first commercial model from Boeing to employ a FBW primary flight control system. In a FBW aircraft there is no mechanical link between the pilot commands and the aerodynamic surfaces: instead, the pilot commands are digitised by multiple position transducers, and a set of computers will issue the appropriate commands to actuators that control the aerodynamic surfaces.

The Boeing 777 flight control system is constituted by two types of components: the Primary Flight Computer (PFC) and the Actuator Control Electronics (ACE) units. The ACE units contain transducers to control the analog command signals and inertial and air data, or analog interfaces to electrically control the electrohydraulic actuators for surface positioning [24]. The PFC is the central

Figure 2.4: MPC563 block diagram. Graphic credit: Freescale Semiconductor.

Figure 2.5: Boeing 777. Photo credit: Boeing.

computation component of the FBW system. All digital flight control components are interconnected by an ARINC 629 data bus, a time division multiplex medium that supports up to 120 simultaneous users.

Triple redundancy for all hardware resources – computing system, electrical power, hydraulic power system and communications system – is used for fault-tolerance in the mission-critical FBW concept, so the PFC, the ARINC 629 data bus and all ACEs are triplicated into Left, Centre and Right flight control systems.

The primary flight control system counts with three PFCs, that provide triple redundant computational channels. All computers are working simultaneously so if one fails, the flight control system can continue its operation without any sort of transient behaviour. Each PFC contains three dissimilar computational lanes, each lane with its power supply and microprocessor and interfaces to the three data buses. Each lane uses a different processor architecture – Intel 80486, Motorola 68040 or AMD 29050 – which leads to dissimilar interface hardware circuits and dissimilar Ada compilers<sup>3</sup>. Each PFC has one computational lane in command mode, and the remaining two lanes monitoring the command lane activity. Any of the computational lanes in a PFC can assume the command mode.

Each PFC and ACE reads data from the three data buses but is only allowed to write on its associated bus, preventing an ARINC 629 transmitter failure or a bus power failure to disrupt more than one data bus. Having access to all buses allow each PFC to monitor the other two PFCs activity and, when detected, decide to through out of service a malfunctioning PFC. On the ACEs side, multiple buses access allows to continue to receive commands, even if its directly corresponding bus is shut down of service.

#### 2.2.4 Industry automation

It has been long since automation mechanisms are employed in the industrial field, but electronics brought a new dimension to versatility and productivity in most industrial applications, from textile manufacturing to metal mining. Diverse scenarios has been leading to diverse approaches and technologies to implement industrial automation solutions.

One technology that is vastly employed in the automation of industrial processes is the *Pro-grammable Logic Controller*. A Programmable Logic Controller is a rugged real-time digital computer designed to control machinery under severe conditions, such as found on factory floors or openair industrial environments. Every Programmable Logic Controller has a set of multiple inputs and another set of multiple outputs which interface with sensors and actuators; usually, these two sets can be modularly customisable by means of interface modules/cards. The processing routine is an infinite loop in which the programme tasks are continuously performed, evaluating the state of inputs and calculating the next state of outputs. Automation solutions based on Programmable Logic Controllers typically aim at applications in which is expected some degree of modifications of the production process along the time (a different programme can be loaded to the device and the sensors/actuators setup can be altered). The modularity of these generic devices allows highly customised automation solutions with products already available in the market, at smaller costs and reduced implementation time, as compared to a specifically designed control system.

The cost of developing a new specific controller system can only be covered by a large-volume application, and it can only be economically effective if the controlled system is not expected to suffer modifications during its operational life-time<sup>4</sup>. In such cases, the controller system may be designed

<sup>&</sup>lt;sup>3</sup>The source code written in Ada by GEC-Marconi (today BAE Systems Electronics Limited) is common in all computational lanes.

<sup>&</sup>lt;sup>4</sup>As an example of such type of systems, one model of a CNC machine tool is supposed to be produced in hundreds or

and packed in a single chip – the *System-on-a-Chip* (*SoC*) – in which the processor core(s), memory, external device interfaces and other hardware components are all integrated in a single integrated circuit, reducing the complexity and dimensions of the printed circuit board and the number of discrete board components. The SoC can be implemented on a Field-Programmable Gate Array (FPGA) – an integrated circuit which is configured after manufacturing, normally by a hardware description language – or, in large production volumes, by an Application-Specific Integrated Circuit (ASIC) – an integrated circuit which is already configured from factory. Software for controller systems based on SoC can range from an application specific programme to a multitasking preemptive OS running multiple concurrent applications, depending on the dimension and complexity of the controlled system. Critical applications may require an operating system with a deterministic real-time scheduler, such as Wind River VxWorks or RTLinux, which assures that concurrent hard real-time tasks will meet the deadlines while executing soft or non real-time tasks in lower priorities.

While generic or specific controllers have an active role in the operation of the controlled equipment, *industrial computers* are used instead to supervise and control the overall system activity. In this sense, industrial computers are not concerned in assisting and controlling the tasks of an individual machine, but rather to monitor the status of specific variables and to be aware of certain events, having a broader-scale vision of the production system. The timing requirements for an industrial computer are not so stringent as the timing requirements that dedicated controllers have to cope, so industrial computers can be managed by non-deterministic OS. Industrial computers have rugged designs and quality computer components to withstand harsh industrial environments: dust-filters, cooling systems and redundant power supplies and data-storage. Some models of industrial computers are equipped with more expansion slots than typically found in desktop computers, to host interface boards that connect the computer to the controlled system components.

#### 2.3 The REMPLI system

The REMPLI project aims to design and implement a communication infrastructure for real-time distributed data acquisition and control operations, exploiting the power grid as the communication medium. The immediate target application is remote meter reading with high time-resolution, being the meters energy, gas, water or heat meters.

The utility companies – the users of the REMPLI system – will have access to detailed information about how the energy is consumed by end-users, so energy flow may be better controlled and leakage can be detected more efficiently. The REMPLI system will be able to determine the actual status of the power grid and can be equipped to remotely terminate supply of energy, if required [25]. Energy billing and energy management are examples of high-level services that can be developed on top of the REMPLI system.

The PLC infrastructure provided by the REMPLI system will allow to access remote metering and control equipment, remaining open to various kinds of add-on services. The schematic architecture of the communication network is illustrated in Figure 2.6.

The REMPLI communications infrastructure can be divided in four segment types:

- low-voltage segments, covering groups of energy consumers;

- medium-voltage segments, between the primary and secondary transformer stations;

thousands of units. Although the set of tasks of the CNC machine is programmable and can be changed several times a year, and the tools used are interchangeable, the controlled machine components – motors, tool turrets – are kept unchanged.

Figure 2.6: REMPLI system architecture.

- TCP/IP- or IEC 60870-based [26] segments between the primary transformer stations and Application server(s);

- TCP/IP communications between Application Servers and correspondent clients.

At the bottom-level of the infrastructure, the REMPLI Nodes are installed at the consumer site. A REMPLI Node includes a set of standard protocol inputs for communications with metering and control devices. Besides the inputs, REMPLI nodes are also provided with outputs capable of switching off and on the supply of electricity/heat/gas/water to a particular consumer, upon commands from the utility company. The Nodes are coupled with a PLC interface in order to connect with the power grid, but they can also be provided with alternative means of communications, like GPRS link.

At the top-level of the infrastructure, the Application Servers of utility companies are connected at the REMPLI Private Network [27]. Each Application Server is responsible for a dedicated function, such as metering, billing or SCADA; some servers may provide processed data to clients located outside the REMPLI Private Network (e.g. Internet, UMTS). An Application Server can access any REMPLI Node using the services of a REMPLI Access Point, a device that performs the gateway between the TCP/IP and medium-voltage PLC segments.

The software architecture of the REMPLI Node allows to execute in parallel different applications, each provided with an interface to the PLC environment. Every application running at the Node is reachable on the other side of the REMPLI system. This way, Application Server(s) can request data collected by a Node application or send commands to the application for self-configuration or to actuate an attached peripheral device [28, 1, 29].

The power-line network consists of one or multiple Low-Voltage segments where the Nodes are located, and one Mid-Voltage segment where the Access Points are installed. Communication at both levels is based in the Master/Slave paradigm. The Medium-Voltage segment is coupled to the Low-Voltage segments by REMPLI Bridges, at secondary transformer stations. The REMPLI Bridge is a device which interconnects a Medium-Voltage PLC slave and a Low-Voltage PLC master. The REMPLI Bridge is completely transparent for Access Point-Node communications, simply forwarding Access Point requests to Nodes and Node responses back to Access Points. In this sense, an Access Point sees all Bridges and Nodes as if directly connected to it, and the communications network becomes a single master/slave communication environment.

#### 2.4 **REMPLI communications architecture**

In actual industrial applications, metering and control devices communicate with application servers using a particular protocol, such as EN-62056-21 or M-Bus (metering applications) or IEC 60870-5-101 (SCADA applications). Application Servers expect to find their respective remote (metering or control) devices directly connected to them, using the referred protocols for communication.

The REMPLI communication system has the objective of tunnelling transparently particular metering and SCADA protocols over the power-line network [2, 30], in such a way that application servers and remote devices do not need to suffer any modification to maintain their regular operations, despite the selected physical network in use. Although the REMPLI architecture allows data transmission over different communications media such as POTS and GSM, the main focus of REMPLI is the PLC.

The communications architecture between a REMPLI Access Point and a single REMPLI Node can be illustrated as in Figure 2.7. This architecture can be easily divided into three logical subsystems: the Access Point Application, the Node Application and the Power-line Communications System.

The REMPLI Node is able to physically connect to metering and control devices, by means of specific hardware interfaces and logical drivers. Each driver is dedicated to a single combination of hardware interface and communication protocol, and is able to handle multiple devices of the same equipment<sup>5</sup>. A driver at the REMPLI Node can perform metering data processing and compressing, in order to reduce the usage of network bandwidth. This processing must be supported by the correspondent REMPLI Access Point driver, so the original data can be reconstructed.

The REMPLI software architecture allows the development and integration of drivers to support additional protocols, as long as they are supported by respective hardware interfaces.

Certain protocols data, like the pulse-based S0 (IEC 62053-31/DIN 43864) cannot be directly transported over the PLC. The architecture of REMPLI nodes allows the development of protocol translators so data originated from one device may be translated to a fully-supported protocol, such as EN-62056-21, understood by metering software on the Access Point side.

The REMPLI drivers at the Access Point side perform the conversion of metering/SCADA protocols received from the Nodes into their TCP/IP-based equivalents. This task can be achieved by simple tunnelling of by standard conversion<sup>6</sup>. As mentioned above, a Node driver may introduce some deviations from the original standard in order to optimise bandwidth usage. These deviations must be undone by the respective Access Point driver, so the tunnelled protocol fully complies to the standard, as seen by the metering/SCADA devices and Application Servers.

The Power-Line Communication System is formed by a set of software and hardware components which are responsible for data transmission over a single-segment (Medium Voltage) or dual-segment

<sup>&</sup>lt;sup>5</sup>For instance, a single M-Bus driver in one REMPLI Node can handle several M-Bus meters, located in one building.

<sup>&</sup>lt;sup>6</sup>As an example of standard conversion, SCADA protocol IEC 60870-5-101 on PLC medium has to be converted to IEC 60870-5-104 on IP network.

Figure 2.7: REMPLI communications architecture over PLC.

(Medium and Low Voltage) power-line networks. The Power-Line Communication System employs a three-layer architecture – equivalent to OSI model transport, network and physical layers – to handle packet-oriented driver-to-driver communication. Metering and SCADA data is requested to Node drivers by Access Points drivers, according to the master/slave model. Protocol requests and replies are transported in Protocol Data Units (PDUs) which are encapsulated into REMPLI network packets from driver to driver.

The PLC System offers fast status transmission, allowing a Node to send fast signalling bits to an Application Server, for internal driver-to-driver communication.

#### 2.5 **REMPLI** software architecture

#### 2.5.1 Software architecture design

As illustrated in Figure 2.7, both Node and Access Point interface with the *Communication System* (in the case depicted, power-line) through two component blocks: the *REMPLI Communication Interface* (RCI) and the *Power-line Adaptation Layer*.

For each medium, a specific set of hardware and software – Communication System – provides functions and services corresponding to Physical and Data Link layers in Open Systems Interconnection (OSI) Basic Reference Model [31].

Adaptation Layers are used to establish a common interface to different types of physical media that may support REMPLI communications, such as power-line, ISDN, POTS or GSM. Adaptation layers implement the functionality [32] corresponding to Network and Transport layers in Open Systems Interconnection (OSI) model, over the respective medium:

- **Delivery of arbitrarily-sized PDU.** Delivery of PDU from the Access Point to a single or multiple Node, and the other way around is the most visible functionality. Communications may be reliable (if delivery fails, the communications system will perform several retransmission attempts before quitting) and unreliable (a transmission failure is ignored). Access Points may unicast, multicast or broadcast data, while Nodes can only broadcast.

- **Concurrent transmission and priority management.** As the Access Point architecture allows several Drivers executing simultaneously, it is possible that multiple PDU may be concurrently submitted for transmission to target Nodes. Each PDU has a priority class associated, which allows scheduling transmissions, according to priority. A higher-priority PDU is always transmitted before any lower-priority PDU, even if it is necessary to suspend a transmission already in progress.

- **Fast status information transmission.** Every Node can set a size-limited bitfield in which all modifications can be quickly propagated to the Access Point, as out-of-band data. Nodes are only allowed to modify their status bitfield, and Access Points can only receive status information.

- **Network discovery.** The REMPLI network is able to report in real-time which Nodes are currently logged in, so it is possible for the Access Point Application to detect potential problems with Nodes and calculate alternative paths to route packets through other Access Points.

- **Point-to-point connection management.** Some communications systems, such as POTS and ISDN require point-to-point connections to Nodes before communications become possible.

The REMPLI Communication Interface is a specification that establishes a common access to the functionality of any Adaptation Layer independently from the communications medium, and is available at Access Points and Nodes, so that applications at both sides may exchange data.

At the opposite side of the communication stack, *Access Point Drivers* have to engage communication with their respective counterparts at the Nodes, in order to satisfy requests issued by possible multiple Application Servers which are connected to the REMPLI Private Network.

*Node Drivers* have mainly to attend Access Point Driver requests, exchanging commands and data with connected meters and SCADA equipment [33].

As the Power-line Communication System provides packet-oriented communication, each PDU is independently addressed and delivered to a specific Node. Apart from network addressing, it is also necessary to address individual drivers at the Node and at the Access Point. This additional addressing is performed in the *De/Multiplexer*, which multiplexes and de-multiplexes communication streams between different pairs of drivers. Additionally, if multiple Application Servers are simultaneously connected to the same driver, De/Multiplexer helps driver to distinguish which incoming response PDU should be routed to which application (request/response identification). The De/Multiplexer component at Access Points is also responsible to handle communication path switching and redundancy: if an Access Point can not reach directly one node, the De/Multiplexer can try to re-route communications through another Access Point which has available a direct communication path to the Node.

#### 2.5.2 Software architecture implementation

The actual implementation of the software concept described in 2.5.1 is within three main software components: *Network Layer*, *Transport Layer* and *Driver De/Multiplexer* [6]. Figure 2.8 illustrates the stack of communication software components found in every REMPLI device – Access Points, Nodes and Bridges. Although these three types of devices share the same communication stack design, making the communication stack at both sides conceptually symmetric, each software component is optimised for the respective device type<sup>7</sup>.

The access to the physical medium is carried by specific hardware. In the case of PLC, it is employed low- and medium-voltage PLC modems, depending on the segment to which the device is connected. The primary task of these modems – corresponding to the Physical layer in the OSI model – is to perform the operations required for data transmission: data coding and modulation. The channel access technique selected is Time Division Multiple Access (TDMA), and Orthogonal Frequency Division Multiplexing (OFDM) as the transmission method [34]. Access to PLC modem functionality and configuration is available to upper layers through a specific device driver.

The Network Layer is responsible for managing the Master/Slave type of medium access in the network [35]. Its main role is to take care of device-to-device communication, mapping to the Network OSI Layer. Still, the REMPLI Network Layer must also manage some LLC/MAC functionality (extending over other lower OSI layers). The Network Layer implements three priority queues to support diverse traffic urgency. Data packets have generally small sizes, to minimise retransmission of long blocks in the case of data corruption by noise degradation, being the maximum fragment size (depending on the configuration) ranging from 40 bytes to 128 bytes.

The REMPLI Transport Layer manages the end-to-end Access Point/Node communications, eventually using Bridges. The REMPLI Communication Interface (RCI) is implemented as part of the Transport Layer, working as the access interface to upper layers. One of the main functions of the

<sup>&</sup>lt;sup>7</sup>E. g. there are three different versions of Transport Layer, one for each device type.

Figure 2.8: Communication software building blocks.

REMPLI Transport Layer is fragmentation (including correct order delivery) mapping directly to the respective OSI Layer. Due to the particular topology of the REMPLI system, communication between Access Points and Nodes via Bridges is managed at the Transport layer level, so the REMPLI Transport Layer must also handle some routing functionality (normally associated to the OSI Network Layer). The Transport Layer includes the following functionality [32]:

- Fragmentation and Bundling.

- REMPLI Node Address / REMPLI PLC address conversion

- Routing (via REMPLI Bridges).

- Support of different Network Layer implementations.

- Retransmission (TCP-like service).

The Driver De/Multiplexer is more connection-oriented and handles not only the redundancy between several Access Points but also the demultiplexing of the Drivers in each end and so it is mapped to the OSI Session layer.